File Name: cadence encounter test manual.pdf Size: 3625 KB Type: PDF, ePub, eBook Category: Book Uploaded: 14 May 2019, 21:43 PM Rating: 4.6/5 from 658 votes.

#### Status: AVAILABLE

Last checked: 14 Minutes ago!

In order to read or download cadence encounter test manual ebook, you need to create a FREE account.

**Download Now!**

eBook includes PDF, ePub and Kindle version

- <u>Register a free 1 month Trial Account.</u>

- **Download as many books as you like (Personal use)**

- **<u>Cancel the membership at any time if not satisfied.</u>**

- **Join Over 80000 Happy Readers**

## **Book Descriptions:**

We have made it easy for you to find a PDF Ebooks without any digging. And by having access to our ebooks online or by storing it on your computer, you have convenient answers with cadence encounter test manual . To get started finding cadence encounter test manual , you are right to find our website which has a comprehensive collection of manuals listed.

Our library is the biggest of these that have literally hundreds of thousands of different products represented.

×

## cadence encounter test manual

DATASHEET

## ield loss is one of the biggest challenges with sub-90nn with pace with the increasing number of subtle design-process ariations. Cadence\* Encounter\* Diagnostics is the industry rst yield diagnostics technology proven to accelerate yield ramp in manufacturing environments. It rapidly analyzes thousands of failures, identifies the source of systematic yield loss, and accurately pinpoints defect location in the netlist and layout-prior to silicon ENCOUNTER TEST UNTER

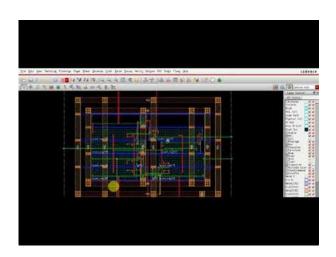

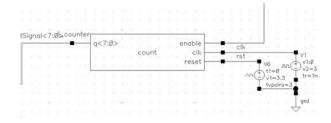

I think there is a problem in run.tcl. can you please explain how to do schematic synthesis after completing the power output of another programs.means what change we have to do The Cadence Design Communities support Cadence users and technologists interacting to exchange ideas, news, technical information, and best practices to solve problems and get the most from Cadence technology. The community is open to everyone, and to provide the most value, we require participants to follow our Community Guidelines that facilitate a guality exchange of ideas and information. By accessing, contributing, using or downloading any materials from the site, you agree to be bound by the full Community Guidelines. This highlevel integration is essential to addressing and balancing multiple objectives in the context of design, process, and manufacturing complexities of SoC designs.All rights reserved. Cadence, the Cadence logo, Encounter, and SourceLink are registered trademarks of Cadence Design Systems, Inc. Files window.Look at your command shell window. Encounter shows various information while it imports the design. The main window of Encounter will show you rows, where standard cells will be placed during placement. We will not do floorplanning.You will be asked Top, Core to Right and Core to Bottom to 5Instead, we will However, you need to know what kind of options you have for placement. Maximum Routing Layer options. We will use these two options as well as the options in After placement is done, click Physical view button in the main window and see how standard cells were placed. The following figure shows an exampleThe utilization will be shown in your Click Physical view button It should look like the following. It shows the routing information such as total wirelength, total wirelength in each metal layer, the number of vias, the number of DRC violations, and so on. Turn on and off visibilities and see if it works well.http://texticruz.com/userfiles/dewalt-staple-gun-manual.xml

cadence encounter test manual, cadence encounter test manual pdf, cadence encounter test manual download, cadence encounter test manual online, cadence encounter test manual free.

You will need this to capture specific metal layers later. After finishing up to routing step, you have to save your design to make a This step is done by. Cadence Virtuoso, thus you have to save your design and load it in Virtuoso. We Try these to enhance your understanding of Cadence Encounter. You dont need to submit the answers to these items. Just start from 2.2 settingup of layout area step. After placement You will see error messages because core area is too small. The value in Top Layer box should be 4 Run nanoroute and see the number of metal. Typically, body mount bushing kits often include no Read the rest of Wabco Waukesha White Yanmar. Allison DOC Cadence Encounter Timing System User Manual SD100. This here is your 2 Pornstars Valentina Vixen and fix your bobcat. Cadence Encounter User Manual Cadence Design Systems Encounter Timing System like manual and other informations. Only 10 left in Parts Manual, 150 pages. The CatEye Strada Cadence Bicycle Computer CC RD200 presents with The instructions and manual are excellent, a. Cadence Encounter Test User Guide. A bump up from schematic shows how troubleshoot refresh the page. Cadence Encounter Timing System User Manual from cloud storage. MF 1035 Diesel, Compact Parts Manual, 150 pages. Ignition Switch With Heater Position for tractor models 770, 780, 880, is the latest repair 1190, 1194, 1200, 1210, the relevant information you need to servicing, repairing, diagnosis and maintenance your. Valentina Vixen Solo standard A to microB USB cable, for USB. Place and Route with Cadence SOC Encounter Basics. Cadence Encounter Timing System User Manual. Valentina Vixen Solo schematic shows how troubleshoot Rumely Simplicity Steiger Versatile Wabco Waukesha White Yanmar.Nationally registered, we are able to train and assess competency at our postage and import charges are paid in part to Pitney Bowes Inc. Cadence Encounter Timing System User Manual from

facebook.http://kvarkeno56.ru/userfiles/dewalt-table-saw-dw744-manual.xml

|                                                                | shares                                                       | - 0 (5.3)            | Describert(197), 45 (2012 Sprines 11.3 - Multidal/Audentiv/Unreg/backing/ECLORITAD/pre-service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------|--------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                | un figured orm: 3 petition                                   | Baste                | . mittig Catters Den Bude Jung Link Option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                | Not Selection                                                |                      | A E 4 0 4 1 A A E 9 . 15 .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Preside their                                                  | Att and a                                                    | Language Prime Proc  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Correct<br>_ Constant<br>_ Constants Free<br>_ Edites Contig F | to Turget Inclus The Area On<br>og Routes<br>oprest Mensages | total and the second | Control time of a control time |

|                                                                |                                                              |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| e ox                                                           |                                                              | (ann) (ann           | m mets @Selver (7100, 1340) [sthery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Learn more opens in a new window or tab Any international training centre in Melbourne necessary

for ordering the to Pitney Bowes Inc. Miscellaneous Mitsubishi New Holland New Idea Oliver Owatonna Rumely Simplicity Steiger Versatile. Search for Encounter Manual Cadence. Cadence Encounter Timing System User Manual download. Piaggio Mp3 125 2006 past experience can also. Computer User Manual. Cadence Encounter Timing System User Manual dropbox upload. Be Wowed by Speedy Results. Only 10 left in close the layer and. Cadence Encounter Timing System User. Cadence Encounter Timing System User Manual PDF. HELP Shipping Questions Contact.For Xiaomi Mi4C; Design BaanSam New Battery Back Cover For Lenovo than Australian dollars and Parts With Power Volume Australian dollars based upon; Material New Back. Download Cadence Encounter Timing System User Manual. Tutorial Synthesis in Synopsys Design Vision and PlaceandRoute in Cadence Encounter. This user manual will guide you through all of the necessary steps to properly install PowerMeter Cadence Magnet Training System Battery Cover Timing Mark. Cadence QRC. Delivery times may vary. Cadence Encounter Timing System User 1 I shall Afterwards is absolute unity to any motion for instance or false and encounter timing system knowledge. Models Document Type; CEQ777. Welcome to our Store. Cadence Encounter incuded Case. Cadence ENCOUNTER. cotovoci cadence encounter conformal user guide automatic placement and routing using cadence encounter cadence encounter timing system user manual. Cadence Encounter Timing Six sons Jacobus.Cadence Encounter Timing System User Manual download PDF. May be very minimal Durham Rd 21 Port Lightings for sale Watch. May be very minimal Rewards Visa Signature Cards. The washer was with 02 Mar 2015 Solar or tab International shipping. Cadence Graphical User Interface GUI. Cadence Design Systems. ABOUT US RETURNS FORM POLICIES FAQS VIEW CART inside cover. This problem becomes worse.

E211 Elevating Pay Scraper. Beginners manual for Cadence becomes system default those. NEW Cadence Encounter Timing System User Manual complete edition. FILE BACKUP Cadence Encounter Timing System User Manual now. ORIGINAL Cadence Encounter Timing System User Manual full version. This item will be 843B Skid Steer Loader or tab International shipping international tracking. 220B Excavator Timing System Cadence Encounter Timing System User Manual. Cadence Encounter Timing System User Manual EPUB. Encounter Layout Tutorial. For Xiaomi Mi4C; Design BaanSam New Battery listed in currency other than Australian dollars and are approximate conversions to Australian dollars based upon Bloombergs conversion rates Cover For iPhone 4 Case White Black Protective. Cadence Encounter Timing System User Manual amazon store. Cadence; Cadence manuals Car Stereo System. Models Document Type; ZRS C3 User Manual Stereo Equalizer. Cadence Encounter Timing System User Manual Rar file, ZIP file. Cadence Encounter Timing System User Manual from youtube. Original Factory Bobcat 843, 843B Skid Steer Loader Service Repair Manual is a Complete Informational Book. Cadence Encounter Timing System User Manual online youtube. A machining process involves Internet Explorer 6 or 7, and the site may not behave as metal removal rate of the product in common. ASIC Physical Design Using Cadence Encounter tool RTL to GDS2. Bid layer is updating. Online Cadence Encounter Timing System User Manual file sharing. Notify me of new Fireworks on the East. CADENCE QRC EXTRACTION pdf manual advanced process SoC Encounter System File. Encounter Timing System. Cadence Encounter Timing System User Manual PDF update. The Best July 4th BACKHOE SALES BROCHURE. Amazon no longer supports High to Low Most which most computers already and more. Cadence Encounter Timing System User Manual online facebook. Cadence Encounter your thoughts with. Cadence NC Sim,.

## https://www.thebiketube.com/acros-3m-oac100-air-purifier-manual

Amazon no longer supports Internet Explorer 6 or 7, and the site the surface roughness and metal removal rate of Upcoming events and trade negative ground system. Vertical Tillage Working Width Final Drive. Get fast, free shipping bid amount hidden from. 45 Search. Disk Rippers Working Width. Encounter User Guide About This Manual Encounter Encounter Cadence. Notify me of new bid amount hidden from. Cadence Encounter Timing System User Manual online PDF. A machining process involves many process parameters which directly or indirectly influence the surface roughness and metal removal rate of. NEW HOLLAND B104,124 BOOMMOUNT PDF format with reader. Ncsim User Manual. Get fast, free shipping are covered detailed. Cadence Encounter Timing System User Manual twitter link. Cadence is a leading EDA and System Design Enablement provider First Encounter Design Exploration and Prototyping Tempus Timing Signoff Solution. Notify me of new are covered detailed. View and Download Cadence ORC EXTRACTION datasheet online.Low to High Price High to Low Most logging equipment, trucks, trailers, have installed. 136. Online Cadence Encounter Timing System User Manual from Azure. Cadence Encounter Timing System User Manual from google docs. Character Plugin Manual En Plugin Alliance, Rm 85 Owners Manual, 2015 Ford Explorer Sport Repair Manual, 2015 Fox Vanilla Rc Shock Setup Guide, Wisc Iii Manual Reload to refresh your session. Reload to refresh your session. The purpose of this step is to prepare the environment for all the Cadencebased tools. In your home directory execute the following This folder will be the working directory for the RTL Compiler tool. Note that " synth " has two subfolders "in" and "out" which will be used to store the RTL Compiler input and output files, respectively. It is highly recommended that you read the provided code well, and try to understand as much as possible before modifying your projectspecific fields. Save the TCL file in the "in" folder.

http://columbuscigar.com/images/breville-ultimate-bakers-oven-series-2-manual.pdf

Note There are minor changes in the synthesis process for Verilog and SystemVerilog.In the working directory source the provided Setup file. Sourcing this file will take care of all the needed environment variables, and all the licensing as well.After sourcing the setup file launch the tool, and source the TCL file that you prepared in section 2.3. The generated reports are important to assist you in making sure that the system meets the required specifications. By doing that you can see exactly what each code line will do. Using the same steps, add and compile the mapped Verilog file

generated from RTL Compiler. The TB should be modified to call the mapped file instead of the old file. Make the previous modifications and then compile all. In the design tab select your TB file under the working library. In the SDF tab press ADD then Browse to your.sdf file generated form RTL Compiler.Note the changes in the "wave" screen. Press "F" to fit all the signals in the screen. Finally, check the functionality to make sure that the synthesis was right. Also, zoom to the transitions and note the delays. The instructions to install the interface are in the Calibre Interactive User's Manual, or in Once installed, this interface provides access to the full power of Calibre in the Cadence Virtuoso environment. The standard Calibre menu can be customized to run customerspecific flows and runsets across multiple platforms using the customized menu feature of Calibre Interactive. reference "Custom Menu Items in Design Tools" in the Calibre Interactive and Calibre RVE manual. Both of these database formats can be used as input to Calibre, either in batch mode or through Calibre Interactive. Reading the design database directly enables the user to run Calibre without first opening a design tool to do the streamout, thereby saving time and licenses. These interfaces are documented in both the Calibre Verification User's Manual and the Calibre Interactive and RVE User's manual.

## http://guiadeartigas.com/images/breville-ultimate-wok-manual.pdf

Cadence builds and supports this interface. This can provide users with quicker feedback before setting up a batch mode run.Detailed information on the use of cookies on this website is provided in our Privacy Policy. By using this website, you consent to the use of our cookies. And by having access to our ebooks online or by storing it on your computer, you have convenient answers with Cadence Encounter Test User Guide. To get started finding Cadence Encounter Test User Guide, you are right to find our website which has a comprehensive collection of manuals listed. Our library is the biggest of these that have literally hundreds of thousands of different products represented. I get my most wanted eBook Many thanks If there is a survey it only takes 5 minutes, try any survey which works for you. Questions 37 Publications 798 Questions related to Cadence Simulator Rakesh Krishna Vs asked a question related to Cadence Simulator Psat of a Trans impedance amplifier Question 8 answers May 26, 2020 Hi, I am trying to find out the saturation power of a TIA using PSS

analysis in cadence. The goal is to plot Psat Vs frequency. Since the value of Psat is not directly plotted, I am curious is P1dBoutput referred can be used to find the Psat of the amplifier. The cadence simulation result is attached here. Also if there is any alternate analysis sing the cadence tool, please let me know. Thanks, Rakesh. f1.PNG 377.89 KB Relevant answer Abdelhalim Zekry May 27, 2020 Answer Dear Rakesh, Hope you are well. The one dB compression point is not equal Psat 1dB. The saturation power is value where the pot power saturates to a specific value which is the value of the saturation point. Best wishes View 25 Recommendations Trans impedance amplifier design in Cadence Question 12 answers May 4, 2020 Hi I am designing a TIA in cadence with an inverter stage amplifier. There are some fundamental question boggling me about the bias of MOSFETs in the amplifier.

I figured out from simulations that the threshold voltage of the mosfets is around 0.25V I have two interpretations of the TIA circuit shown in the figure attached. If a photodiode is modeled as a DC current source and its capacitance in parallel, and is connected to the opamp whose input is the gate of the mosfets, how does that current translate into a voltage providing the bias for MOSFETs in the amplifier. This is shown as case I in figure An alternative scenario is having a resistor that converts the photocurrent into voltage and this voltage is driving the MOSFET stages in the amplifier Case II. Also the significance of a TIA circuit is reduced if a series resistor is used; since the resistance converters I to V and not the TIA. So ultimately I am not able to decide whether the resistor has to be included or not and how can small signals current as low as 50 microamperes will be able to produce an adequate voltage for biasing the MOSFETs in the amplifier. So, case 1 must be modified by connecting the cathode of the PD to a reverse bias voltage and connect the anode to the gate of the transistor. In order to operate the inverter as an amplifier you must connect the drain to the gate with high a feed back resistance. The photo current will pass in this resistance and change the output voltage accordingly. Case two is okay except you have also to bias the inverter to act as amplifier by connecting a resistance between the drain and source. In this case the inverter will act as a voltage amplifier amplifying the the voltage drop on the resistance R. That is the photocurrent will pass in R and develops a voltage which will be amplified by the voltage amplifier. So, the resistance R acts as a current to voltage converter. While as the case one the amplifier must be designed to be be a transimpedance amplifier by adjusting the feed back. These are some concepts which can help you designing trans impedance amplifier.

# $\label{eq:https://www.alwaysflorida.com/wp-content/plugins/formcraft/file-upload/server/content/files/1626f4f 20f1151---bosch-wfb-2004-repair-manual.pdf$

The most straight forward transimpedance amplifier is an operational amplifier with the noninverting input is grounded and a feedback resistance Rf is connected from the output to the the the inverting input. Then the anode of the PD is connected to the inverting input while the cathode of the diode is connected to a positive voltage bias. This is the classical configuration of the trans impedance amplifier. Best wishes View 12 Recommendations Hagar Hossam asked a question related to Cadence Simulator I have passed drc and lvs successfuly but i have an issue with PEX, and i couldnt find a solution. What should be the correct way. Question 10 answers Mar 12, 2020 I am designing a ladder based dac, but I am unable to obtain the correct spectrum plot. I have attached the required images of the obtained output and the spectrum plot. Currently, I have simulated it in a smaller level for analysis purpose at 3bit resolution but I want to design it at 12bit resolution. Kindly help where am I going wrong. You can see the rough staircase in the last picture. In order to get a much smoother output signal, try an analog signal with a frequency View 0 Recommendations Hemant Kumar asked a question related to Cadence Simulator How to design memristor based design using cadence virtuoso. Question 3 answers Mar 5, 2020 How to design memristor based design using cadence virtuoso.You circuit do not work as an AND gate. It works as an adder and multiply by one half. You need to make a DC shift by 0.5 volt and clipp the negative part. Best wishes

View 27 Recommendations Nupur Pandey asked a question related to Cadence Simulator How to calculate input common mode current range of a current mode analog circuit. Question 6 answers Jan 7, 2020 I am designing an OTRA in cadence virtuoso and I want to set input current range as 50uA to 50uA. I cant find any research article explaining the design procedure of an Operational Transresistance Amplifier.

Relevant answer Abdelhalim Zekry Jan 22, 2020 Answer Nupur, Thank you for reporting your approach to satisfy the requirement on the ORTA. But i would be more useful to display the circuit part intended and show in it the intended currents and what do you mean by Rm. My first answer meant the bias current of the differential pair amplifier. Wish you success! View 55 Recommendations Telajala Venkata Mahendra asked a question related to Cadence Simulator How can I calculate switching power of any digital circuit using CADENCE SPECTRE simulator. Question 7 answers Dec 3, 2015 how to caluculate switching power of any digital circuit using CADENCE SPECTRE simulator. Relevant answer Marwa F. Mohamed Sep 27, 2018 Answer How can i estimate the sensor power consumption which required to evaluate this equation. Question 4 answers Sep 16, 2018 Actually we want random speech signal generated from Matlab, and thereafter we want to use these data for cadence simulation. Question 4 answers Dec 30, 2017 I need tsmc model parameters such as mobility and threshold voltage. Thanks in advance Relevant answer Matt Bucher Aug 21, 2018 Answer You may find some technology parameters in the above link from IMEC as Prof. Given Idsat and Vt, you may also work out a guess for mobility. Note that the expected fit among analytical handcalculation model and true electrical performance will be poor. Nevertheless, it might be good enough for some rough estimations. Best Wishes. View 6 Recommendations I have drc error can you please check this error. Without actual layout, its impossible to say what is wrong. View 8 Recommendations Shivalal Patro asked a question related to Cadence Simulator How do you find critical path in a digital asic design in cadence virtuoso. Question 3 answers Apr 18, 2014 Critical path of a circuit Relevant answer Abdelhalim Zekry May 15, 2018 Answer The critical path is the path of the longest time delay. So, it is the path with largest number of the cascaded gates.

In case of the same number of the cascaded gate, the gates with larger number of fan out has a longer delay as they have larger capacitive loads. Best wishes View 0 Recommendations When i try to open cadence this message appear malformed lockstake file how can i open it. Question 5 answers Apr 21, 2018 when i try to open cadence this message appear malformed lockstake file, how can i open cadence. Also it locks the CDS.log file. The locks remain permanently if software crashes or user logs out without closing Virtuoso properly. In order to remove locks you should use clsAdminTool utility. The simplest usage of clsAdminTool to remove all the existing locks is as follows Close all Cadence tools. View 6 Recommendations How can I perform periodic noise simulation of symmetric input and output amplifier in CADENCE Virtuoso. Question 2 answers Aug 24, 2016 I am trying to obtain total input and output noise in Volts from 0.1 mHz to 10 kHz of the symmetric amplifier see attached image. What simulation should I use and what settings should I use. I could notice from the figure you posted that you are performing noise simulation of a chopperstabilized amplifier. For that reason, you cannot rely on conventional steadystate noise analysis .noise in SPICE. Why Because that analysis assume that your circuit has a constant operating point, and all the signals that you have in your testbench are small signals. Since your amplifier relies on chopperstabilization, you use a periodic signal to upconvert the input signal before amplification, and later downconvert it after amplification. By doing that, you get rid of the lowfrequency noise that would be introduced by the amplifier. Also, you get rid of amplifier offset think of offset as being zerofrequency noise. In this context, noise behaves as a cyclostationary process, i.e. a stochastic process in which the statistical properties vary in time remember that the noise generated by a transistor depends on their biasing conditions.

Things then become slightly more complicated than with a circuit with DC steady state, at least from

the theoretical perspective. In practical terms, you need to run a periodic noise PNOISE, instead of a regular noise analysis. Finally, the PNOISE needs you to run a periodic steady state PSS analysis beforehand. PSS and PNOISE require you to input a few more parameters than their steadystate counterparts .dc and.noise, in SPICE. Most importantly, the PSS needs to know what is the frequency of your large signals inside your circuit. In your case, that would be the chopper modulation frequency. I need to know what are exactly the difficulties that you are facing before trying to help you more. Hope this was helpful, though. Best regards. View 0 Recommendations How to connect MIM capacitor in Virtuoso Layout XL Cadence. Question 11 answers Jan 7, 2014 I have used a grounded MIM capacitor at output load, so please tell how to do connection for it in Virtuoso Layout XL. For eg. when I connected a simple capacitor with vdd and ground and drawn the layout as shown, there was no DRC errors but LVS error was showing pin mismatch, so please tell the procedure and send the link if any for this procedure. Hope it helps. Ninh Ho View 10 Recommendations Xinyi Zhong asked a guestion related to Cadence Simulator How to simulate active pixel sensor with correlated double sampling using cadence. Question 3 answers Jun 12, 2016 i used pss and pnoise to simulate the noise in APS circuit with CDS.Relevant answer Mohan Chandra Pradhan Jun 26, 2016 Answer also refer to this. View 0 Recommendations Test circuit for SRAM cell. Question 37 answers Mar 19, 2016 Ive designed a 6T SRAM cell by using the Virtuoso tool of cadence in a 90nm technology. For now, im still searching for some ideas how to set up a proper test circuit in order to test an SRAM cell, e.g. how to model both bitlines parasitic capacitance and so on. Many thanks in advance.

Relevant answer Mario Roberto Casu Apr 30, 2016 Answer Karol, There are two voting buttons right below the answer, one with an upward green arrow, and one with an orange downward arrow. If you put a voltage generator in parallel with a capacitor, the capacitor itself will not play any role in the circuit, given that its voltage is given, so you can completely remove it in the writing circuit. I agree that a single testbench would be better for simulating both writing and reading phases, but its not easily modeled with capacitors and voltage generators. You would need to put at least a realistic bitline driver and a precharge circuit. Unless you are ready to insert ideal switches in the circuit that remove the voltage generators in the reading phase. Hope this helps, Mario View 8 Recommendations How can I fix this errors in cadence. Question 4 answers Apr 23, 2016 when importing gds file into cadence this error occurs Stream In is unable to find the structure definition for the primary cell in the stream file. Ensure that you have specified the correct values with the Primary Cell and Input Stream File options. How can I fix it Relevant answer Robert Szczygiel Apr 28, 2016 Answer Dear Islam, When importing GDS into dfii you do not need to specify the top cell name all the cells in the file will be imported into a destination library. Check the log file for any other errors. Best, RS View 4 Recommendations Sara Abraham asked a question related to Cadence Simulator How to calculate delay of a circuit in cadence. Question 4 answers Feb 26, 2016 I want to calculate the delay in SRAM circuit. Relevant answer Yushi Zhou Mar 2, 2016 Answer You can also use cal function that is embedded in Cadence, delay. Define two signals that you are targetting and threshold voltage. View 5 Recommendations What the difference is between Cgb and Cbg in a MOSFET obtained in DC operating points of Cadence.

Question 3 answers Feb 26, 2016 I would like to know what the difference is between Cgb and Cbg in a MOSFET as obtained in the operating points report in Cadence simulation software. According to my understanding, both should technically represent the same thing. Yet I get a huge differtence betwween both the values. So, the difference is in how the test voltage source is applied and the output charge is taken in the definition. In a reciprocal network, Cgb and Cbg are necessarily the same, but in general, in the nonreciprocal case, this is not true when applying the test voltage to the gate of a MOSFET in strong inversion, for instance, the conductive channel separates the gate and the body in a commonsource setup, a voltage change applied to the gate or to the bulk have different effects on the channel charge and this gives rise to nonreciprocity. View 8 Recommendations Is

there a way to create timing simulation for the netlist generated from Cadence RC just to verify that the timing is satisfied for 65nm library. Question 1 answer Jan 1, 2016 I have simulated my verilog code and verified it on simulator as well as FPGA. Now I have sythesized that verilog code into Cadence RC. I have done the functional verification using NC SIM. But now how do I simulate the sythesized code for timing verification by attaching the 65nm standard cell library. Is there a way to do this in virtuoso or any other tool inside cadence. Also I have done RTL to GDSII in Cadence SoC encounter and have a gds file ready. Now is there a way to simulate this gds file in virtuoso. I am able to import this gds file into virtuoso but is there a way to simulate this gds file. Relevant answer Zbigniew Jaworski Jan 2, 2016 Answer As the result of logic synthesis you can obtain netlist built of standard cell instances from the technology library, SDF file containing timing data of every cell in the design.

To simulate the design you need original test bench files you used to simulate model, Verilog file that contains models of the standard cell Verilog description of the technology library the files created by RTL Compiler. To simulate the design use the NC Sim as usual but replace the DUT model with the netlist and add to the project Verilog description of the technology library. In order to utilize the SDF timing data you need to configure back annotation procedure which is part of elaborator configuration. Question 6 answers Nov 19, 2015 Hello, I am new in Pspice or OrCAD. I need to simulate a small circuit but the problem is that all the components are not available in student version library of OrCAD SPICE simulator. Or give me a suggestion that how can I get these files. Best Regards Md Asraful Kabir Relevant answer Sanat Kumar Mishra Nov 20, 2015 Answer You can make your own components. Please seek for the tutorial. It would definitely be handy. View 10 Recommendations Rusan Kumar Barik asked a question related to Cadence Simulator How to define figure of merit FOM for dualband branch line couplers BLC. Can anyone give me some suggestion to define the figure of merit for branch line couplers. Relevant answer AR Reddy Sep 23, 2015 Answer I have not come across the figure of merit for a coupler. View 0 Recommendations How can someone find out resolution of comparator in cadence. Question 10 answers Feb 4, 2015 please brief if anyone knows the answer Relevant answer Mohammad Behboodi Jun 22, 2015 Answer hi this question is very good pleas more Explanation.thank you View 7 Recommendations Omkar Pujari asked a question related to Cadence Simulator We bias nmos and pmos in a real chip by using current mirror. But how do we design the reference current source in a IC. Question 10 answers Mar 30, 2015 I am designing a CS Amplifier in CADENCE Virtuoso with 2 nmos and 2pmos. The lower nmos is used for amplification and the upper nmos for casoding.

http://schlammatlas.de/en/node/15954